## Real Time Zetta Bytes -Universal Memory ASIC SOC IP Core Design Implementation using VHDL and Verilog HDL for High Capacity Data Computing Processors like Cloud/Cluster/Super VLIW Parallel Distributing Pipelined Array Computing Processors

P.N.V.M Sastry <sup>1</sup>, Dr.D.N.Rao<sup>2</sup>, Dr.S.Vathsal<sup>3</sup>

<sup>1</sup>(Professor & Dean -Real Time It Eda Software Mnc Industry & R&D Cell &Ece,J.B.R.E.C, India)

<sup>2</sup>(Former Principal –J.B.R.E.C & Professor & Head -Ece ,Dean R&D, J.B.I.E.T, India)

<sup>3</sup>(Former Dean R&D – J.B.I.E.T & Professor – Eee, I.A.R.E, India)

Abstract: The main intention is RTL Design Architecture and HDL Design Implementation of Zetta Bytes Memory ASIC SOC IP Core for Advanced Parallel Array Distributed Pipelined Array Computing /Cloud Computing / Super VLIW Computing/Cluster Computing Processors/very High Big Data Control Stations /Servers, Arrays of Data Servers, Interfacing for All Advanced Real Time Smart Computing Products-wireless, telecom, consumer, advanced processor and controller IP cores, Aerospace/Avionics, Automotive, Industrial Automation, Hi-Fi applications. Design Coding Implementation Done by Verilog HDL and VHDL, Simulation and Synthesizing, FPGA Front End Design Flow Implementation Done By Xilinx ISE 9.2i Software. Programming & Debugging Done through Xilinx Virtex/Kintex-7 FPGA Development Board/Kit.

**Keywords:** Application Specific Integrated Circuit, FPGA – Field Programmable Gate Array, HDL – Hardware Description Language, ISE – Integrated Software Environment.

### I. Introduction

In Modern electronics Memory Plays vital role in all advanced real time smart Embedded computing products and applications for keeping large storage of data of Big Big Data Centric Storage and controlling Applications like Stations and Servers, Cloud, cluster, Parallel Distributed Pipelined Array Processors Computing and large data Storage Servers and Racks and Network Array Processors Computing, Graphics and Large Data Image Processors Computing. Now I Designed Universal Memory IP ASIC SOC IP Core of Different Data bytes capacity- Zetta bytes capacity Memory IP Cores. The Memory SOC IP Core Store Large secure Big Data of Big MNC's/ Large Defense Sectors/Entire Major network and storage stations /cities etc. This memory IP Core is very suit for all Advanced ASIC.FPGA Development Boards . This memory IP Core is virtual type. This memory is very suit for future advanced applications and 6<sup>th</sup> Sense Products . This Memory ASIC Contain RTL Blocks of Zetta Bytes Memory Design Blocks. This Memory acts as a Universal IP Core for Both RAM and ROM Array Designs. This Memory Contains Chip Select CS Signal, Read and / Write Control Signal and Zetta Bytes Data. For Zetta Memory -2<sup>70</sup> Data Bytes Storage Locations for advanced HIFI Real Time Smart-Computing-Industrial-Software-Applications / Products. These memories are purely clock dependent storage. This Memory Contains 8/16/32/64/128 Data Bit Storage Width for that I 'am using Registers for keeping temporary/Permanent storage of Data. The Main Intention of Designing the Universal memory SOC ASIC Soft IP Core is for At a time computing and running the functionality of multiple large big Data by based Control Stations/Servers /MNC's Servers by Partitioning Big Memory spaces using Parallel Array Distributed Computing Array Technique and Cloud/ Cluster Computing Technique using Single System on Chip Solution. This-Memory-suit-for-Interfacing-with Advanced Processor Boards of Mega /Giga /Tera /Peta /Exa /Zetta /Yotta /Xona /Weka/Vendica Bytes Capacity and Same Frequency Rate Baud rate Generators for Out rich Electronic Design Cards/SOC's.

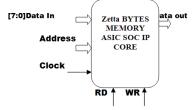

# II. Zetta Bytes Memory Design Architectures 1.1 Zetta Bytes Memory Asic Soc Ip Core Design Architecture/Block Diagram

Fig(1). Zetta Bytes Block Architecture

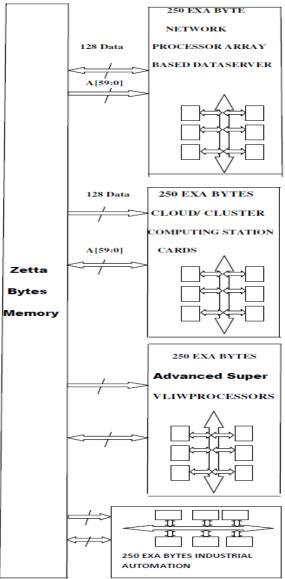

### 2.2 Zetta Bytes Memory Detailed Architecture

DOI: 10.9790/0661-1805030108

Fig(2). Detailed Memory Interface Partition Soft IP Core Architecture

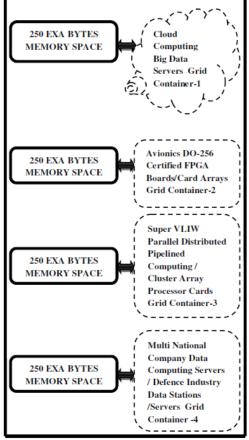

2.3 Description. Zetta Bytes Memory Partitioned Into four 250 Exa Bytes Memory. Each having 128 Bit DataBus and 60 bit Address bus and Each Exa byte Memory Allocated for Network Processor Array Based Data Servers Card, Cloud/Cluster Computing Station, Advanced Super VLIW Processor Array Cards, Industrial Automation Products / Application Cards. Each Share Data and Address through Data Bus and Address Bus. This is mainly Designed for Processing, Controlling, Maintaining Big/Large Secured Data . Splitting the Data in to Sub Data for Different Card Array Based Busses. And This Memory Running Large Data and Applications through Advanced VLIW Processor Instructions through Advanced Network Data Servers, Cloud/Cluster Computing Stations, Advanced Super VLIW Processor Array Cards for Running Long Instruction Words through Parallel Pipe Line Array Distributed Computing Array Technique like Fetch, Decode, Execute the Data Functionality in the Memory Partitioned Space. Simply These Are Executed through Pipelined Processors Cloud/Cluster Array Cards. Data Rate In terms of Zetta Bits Per Second through Zetta Hertz Clock. This Clock Synchronizes all Big Data Frames/Packets d Processing and Controlling. Processing in terms of Bytes, Frames, Super Frames, Super Very Long Word Frames for Highly Reliable Data Computing in these Memories. And Also other remaining 250 Exa Bytes Memory Space for Running the Applications / Products Industrial Automation Applications Real Time Smart Computing Applications like wireless and telecom protocols, Transceivers, Highly Reliable Consumer Electronic Smart Computing Products ,Image and Medical Diagnostic Products /Applications, Image and Graphics Processing and Computing w.r.t Clock Synchronization. This is simply Single System on Chip Card Solution.

# 2.4 zetta Bytes Memory System-Asic Soc Partitioned Interface Architecture

Fig(3). Zetta Memory System Partitioned Software IP Core Architecture

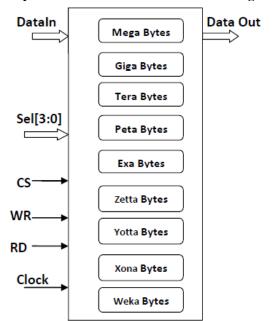

### 2.5 Universal Memory Asic Soc Ip Core Detailed Architecture/Block Diagram

Fig(4).Detailed Architecture Universal Memor Asic Soc

**2.5.1Description.**This Soft IP Core Universal Memory Chip Contains Different Data Byte Memorieslike Mega,Giga,Tera,Peta,Exa,Zetta,Yotta,Xona,Weka,Vendica Bytes Capacity for Processing, Storage, Controlling, Distributed Large Computed Big Data Applications/Products

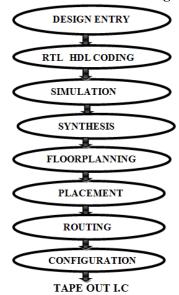

### III. Software – V.L.S.I I.C Design Flow

Fig(5).VLSI Design Flow Chart 2e<sup>23</sup>-1 E.b.p.s P.R.B.S A.S.I.C I.P CORE

**Description.** The Design Process and Implementation Done by the above V.L.S.I Software Design Flow Chart Phases. It Consists Design Entry Specifications , R.T.L H.D.L Coding (V.H.D.L and Verilog H.D.L) and R.T.L Logic Simulation and R.T.L Synthesis and Floor planning, Placement and Routing of  $2e^{23}$ -1 E.b.p.s P.R.B.S A.S.I.C I.P CORE Implementation Done by Xilinx FPGA Synthesis Software (X.S.T)

### IV. Fpga Design Flow Reports

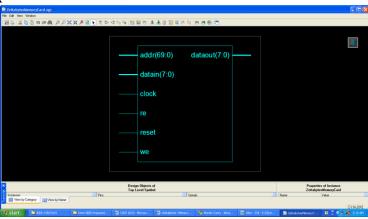

### 4.1 Rtl Design Block

Fig(6). Zetta Bytes Memory RTL Design

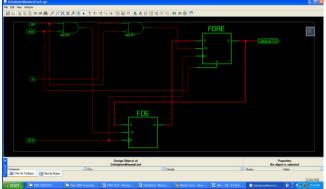

### 4.2 Zetta Bytes Memory RTL Schematic Design Block

Fig(7). Zetta Bytes Memory RTL Schematic

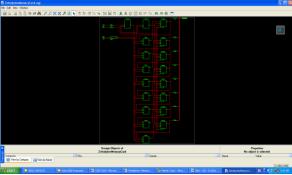

### 4.3 Zetta Bytes Memory Technology Schematic Block

Fig(8). Zetta Bytes Memory Technology Schematic

### 4.4 Zetta Bytes Memory FPGA Placed Design Report

Fig(9). Zetta Bytes Memory FPGA Placed Design Report

### 4.5 Zetta Bytes Memory FPGA Routed Design Report

Fig(10). Zetta Bytes Memory FPGA Routed Design Report

### IV. Hdl Synthesis Report

### Macro Statistics

| # Registers           | : 2  |

|-----------------------|------|

| 8-bit register        | : 2  |

| Final Register Report |      |

| Macro Statistics      |      |

| # Registers           | : 16 |

| Flip-Flops            | : 16 |

|                       |      |

### Final Report

9 out of 1920 0% Number of Slices: Number of Slice Flip Flops: 16 out of 3840 0% Number of 4 input LUTs: 2 out of 3840 0% Number of IOs: 90 Number of bonded IOBs: 12% 12 out of 97 Number of GCLKs: 1 out of 12%

### TIMING REPORT

### RTL Top Level Output File Name ZettabytesMemoryCard.ngr

Output Format : NGC Optimization Goal : Speed Keep Hierarchy : NO Design Statistics # IOs : 90 Cell Usage: # BELS : 2 : 2 LUT2 # Flip-flops/Latches : 16 # FDE : 8 # : 8 **FDRE** # Clock Buffers : 1 BUFGP : 1 # IO Buffers : 11 **IBUF** : 3 **OBUF** : 8

### Device utilization summary: Selected Device: 3s200tq144-5

Number of Slices: 9 out of 1920 Number of Slice Flip Flops: 16 out of 3840 0% Number of 4 input LUTs: 2 out of 3840 Number of IOs: 90 Number of bonded IOBs: 12 out of 97 12% 1 out of 12% Number of GCLKs: 8

### TIMING REPORT

### Timing Summary:

------

Speed Grade: -5 Minimum period: 1.547ns

(Maximum Frequency: 646.224MHz)

Minimum input arrival time before clock: 3.889ns

Maximum output required time after clock: 6.280ns

Timing constraint: Default period analysis for Clock 'clock' Clock period: 1.547ns (frequency:

646.224MHz)

Total number of paths / destination ports: 16 / 16 Total memory usage is 143912 kilobytes Reconfiguration/ FPGA Programming Window

### V. Real Time Live Applications

# Cellular Base Station C Components Power Supply Fiberlink Transmission Corponents - Station Cypledectorics Cypledectorics Cellular Phone Cellular Phone

### VI. Conclusion

Zetta Bytes Memory Designed for Large Computing Data Stations like Servers/Cloud Computing, Advanced VLIW Parallel Distributed Computing Processors , High Speed Industrial Data Automation Systems.

### **Bibliography**

M.S(E.C.E)(A.U), M.Tech(E.C.E), (PhD)-ECE(JNTUH), PG Dip.VLSI(I.S.O.U.K, B'lore)

Prof.P.N.V.M Sastry Currently working with a Capacity of Dean- I.T E.D.A Software Industry CELL &

R&D CELL & ECE DEPARTMENT, He Did Master Degree In Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU -1998.Did PG Diploma In V.L.S.I Design ,I.S.O.U.K.A.S Certified From V3 Logic Pvt Ltd, Bangalore-2001, Did M.Tech (ECE) From I.A.S.E Deemed University-2005. Currently Pursuing (Ph.D)-E.C.E(V.L.S.I) , J.N.T.U Hyderabad -2012 , Over Past 17 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate -CYIENT

(INFOTECH), ISiTECH as a world top keen IT Industrial Software Specialist – World Top Software Engineering Team Leader(Level 6) Eng-Eng- HCM Electronics Vertical & Sr. Program Manager -EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hi-tech Software Engineering Verticals & Departments & I/C M.F.G Hi-tech Eng.Software Vertical , Program Lead - Embedded & VLSI & Engineering Delivery Manager - IT Semiconductor Software Engineering Vertical ,at ISiTECH , also worked with Govt R&D, Industrial Organizations, Academic Institutions of Comparative Designations & Rolls . His Areas Of Interest are V.L.S.I -V.H.D.L, Veirilog H.D.L, A.S.I.C, F.P.G.A & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, I.T Software M.N.C Board Meetings(Tier1/2 Level MRM-V.P,C.O.O Level), Guided R&D, Industrial, Academic Projects /Products -VLSI-ASIC,FPGA & Embedded & Embedded, V.L.S.I Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At CYIENT( INFOTECH) as a Program Manager & I/C- MFG Eng Software Vertical and Dept. Under Sr. Vice President Mr. Jagan Mohan Venneti, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various 41 International Journals of Reputed Journals and Conferences also Certified Conference Chairs - ,I.T.C. I.D.E.S- MC GRAWHILL EDUCATION-Chennai & I.E.E.E -C.S.N.T.- Gwalior & Best Paper Award On behalf of Exa Hertz Wi-Fi Router A.S.I.C Paper at I.S.S.R.D-I.C.S.C.D SANDIEGO, U.S.A., Accepted Journal at High Reputed Journal - Mitteilungen Klosternburg Weiner Strasse, AUSTRIA, Europe etc.), and also J.M.E.S.T - Germany . Judge for Various Paper Presentations like IEEE-CBIT, JBREC Conferences, Workshops etc. Recently Invited me as a Reviewer of IEEE TENCON-16, Singapore.

Dr. D.N Rao B.Tech, M.E., Ph.D., earlier principal of JBREC, Hyderabad. And Professor & HOD JBIET, His

carrier spans nearly three decades in the field of teaching, administration, R&D, and other diversified in-depth experience in academics and administration. He has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities

Dr.Vathsal Currently working as a Professor & Dean- R&D & EEE, JBIET, He Obtained PhD from

I.I.S.C.Bangalore, also Did Post Doctoral Research in DFVLR, Germany and NASA Goddard Space Flight Centre, USA, and also he worked with keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He Published lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India.