## Design and Analysis of Carry Look Ahead Adder Using CMOS **Technique**

# Amita<sup>1</sup>, Mrs. Nitin Sachdeva<sup>2</sup>

$^{1}$ (Electronics Engineering Department/YMCA University of Science and Technology, Faridabad)

Abstract: Addition is a fundamental operation for any digital system, digital signal processing or control system. In this paper we have designed a carry look adder circuit using CMOS technique. The propagation delay is one of most important problem in the adder circuits. So the delay problem of Ripple carry adder is analyzed by CLA adder. The adder circuits are designed using Tanner EDA tool and simulation is done by T-Spice 180nm technology. The ripple carry adder and Carry look ahead adder is compared in terms of power and delay. By the analysis of adder circuits using tanner tool found that the delay of proposed carry look ahead adder is reduced 34%. Hence it gives better performance that ripple carry adder.

Keywords: Carry Look Ahead Adder, CMOS technique, Ripple Carry Adder, Propagation Delay, Power dissipation

#### I. Introduction

ALU is the fundamental building block in central processing unit. ALU needs adder circuit for addition and multiplication. In the past major challenges for VLSI designer to reduce the area of chip. Now three major performance parameters i.e. Power, area and speed are focused by VLSI designer. A carry look ahead adder is a type of adder used in digital logic. It improves speed by reducing the amount of time required to determine carry bits. It can be contrasted with the simpler, but usually slower, ripple carry adder for which the carry bit is calculated alongside the sum bit, and each bit must wait until the previous carry has been calculated to begin calculating its own result and carry bits. In this paper Carry look ahead adder is designed and analyzed using standard CMOS technique. Tanner simulation has been done for 180 nm technology to determine power dissipation and delay. Carry look ahead adder is compared with ripple carry adder.

#### Design Of Carry Look Ahead Adder and Ripple Carry Adder

Carry look ahead adder:

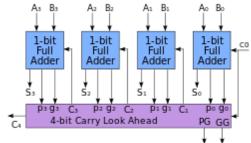

The basic block diagram of carry look ahead adder is discussed in this. The carry look ahead adder using the concept of propagating and generating the carry bit. It calculates one or more carry bits before the sum, which reduces the wait time to calculate the result of the larger value bits.

Fig 1: Block diagram of 4 bit carry look ahead adder

The expression for Carry propagate,Pi = Ai xor Bi

Carry generate, Gi = Ai . Bi

Sum expression, Si = Pi xor Ci Carry out, Ci+1 = Gi + Pi Ci

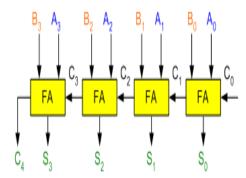

Ripple carry adder:

A ripple carry adder is a logic circuit in which the carry-out of each full adder is the carry in of the succeeding next most significant full adder. It is called a ripple carry adder because each carry bit gets rippled into the next stage. In a ripple carry adder the sum and carry out bits of any half adder stage is not valid until the carry in of that stage occurs.

<sup>&</sup>lt;sup>2</sup>(Electronics Engineering Department/YMCA University of Science and Technology, Faridabad)

Fig 2 Block diagram of ripple carry adder

#### III. Technique Used

The most widely used logic style is standard CMOS. Complementary metal oxide semiconductor (CMOS) is a technology for constructing integrated circuits. CMOS circuitry dissipates less power than other logic families with resistive loads. Since this advantage has increased and grown more important.

#### IV. Performance Parameters Of Design

#### a) Power dissipation:

Power dissipation is a measure of the power consumed by the logic gate when fully driven by all its input. The D.C or average power dissipation is the product of D.C supply voltage and the mean current taken from the supply. We can compute the whole power dissipation through the following equation-

P total = P static + P dynamic + P short cir P =  $\alpha$  CL Vdd2 fclk( Isc + I leakage)Vdd

#### b) Propagation delay:

The propagation delay can be defined as time required to reach  $0.5~V_{dd}$  of output from the  $0.5~V_{dd}$  of input. The propagation delays of Carry look ahead adders are measured in orders of nanometers. This is the important factor in CLA design. The propagation delay of carry bit is calculated. The speed of adder is depending upon propagation delay how fast circuit is work.

#### V. Simulation And Results Of CLA And RCA

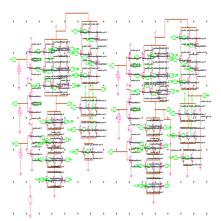

All the simulated circuits of carry look ahead adder and ripple carry adder are given. The comparisons of 2 bit carry look ahead adder and ripple carry adder are done by channel length 180nm technology. Power dissipation, Propagation delay are calculated and compared. Carry look ahead adder:

Fig 3 Schematic of carry look ahead adder

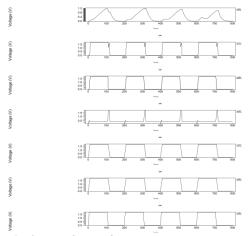

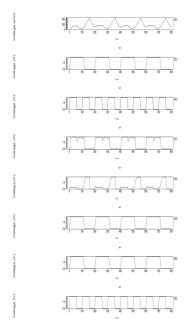

#### **WAVEFORM:**

Fig 4 Waveform of carry look ahead adder

Ripple carry adder:

Fig 5 Schematic of ripple carry adder

### **WAVEFORM:**

Fig 6 Output waveform of ripple carry adder

#### Simulation results of carry look ahead adder and ripple carry adder using 180nm technology

| DESIGN       | AVERAGE     | DELAY(s   |

|--------------|-------------|-----------|

|              | POWER(watt) | ec)       |

| CARRY LOOK   | 1.369*10^-3 | 3.187*10^ |

| AHEAD        |             | -8        |

| RIPPLE CARRY | 4.871*10^-4 | 4.857*10^ |

| ADDER        |             | -8        |

Table1

#### VI. Conclusion

The proposed carry look ahead Adder is designed using CMOS technique and it performed with 34% less propagation delay as compared to ripple carry adder. The no of transistor count increases but gives less delay and high speed. The carry look ahead adder is used as propagation adder in various multipliers and gives less delay. For future work these high speed adders are used in multiplier circuits.

#### References

#### Journal papers:

- [1] JagannathSamanta, MousamHalder, Bishnu Prasad De "Performance Analysis of High Speed" low Power Carry Look-Ahead Adder International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-2, Issue-6, Jan- 2013

- [2] Fu-Chiung Cheng Stephen H. Unger "Delay-Insensitive Carry-Look ahead Adders"

- [3] KaammnRaahemifar,MajidAhmadi "fast carry-look-ahead adder" Proceedings of the 1999 IEEE Canadian Conference on Electrical and Computer Engineering Shaw Conference Center, Edmonton, Alberta, Canada May 9-12 1999.

- [4] ManojKumar,Sandeep K. Aryaand SujataPandey "Single bit full adder design using 8 transistors" International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.4, December 2011.

- [5] ChetanaNagendra, Marry Jane Irwin "Area, Time and power Tradeoffs in Parallel Adders".

- [6] F.C.Cheng, S. H. Unger, M. Theobald, and W. C. Cho, "Delay-Insensitive Carry-look ahead Adders", VLSI Design Proceedings, pp. 322-328, 1997.

- [7] M.C.B. Osorio, C.A. Sampaio, A. I. Reis, R.P. Ribas., etc.al. "Enhanced 32-bit Carry Look ahead Adder using Multiple Output Enable-Disable CMOS Differential Logic". SBCCI, pp. 181-185, 2004.

- [8] K. Ueda, H. Suzuki, K. Suda, H. Shinohara, K. Mashiko,et.al., "A 64-bit Carry Look Ahead Adder Using Pass." IEEE Journal of Solid-Stale Circuits, vol. 31, no. 6, pp. 810-818, 1996.

- [9] Wei, B. W.; Thompson, C. D.; "Area-Time Optimal Adder Design", Computers, IEEE Transactions on, Vol. 39, No. 5, May 1990, pp. 666-675

- [10] V. Kantabruta, A recursive carry-lookahead/carry-select hybrid adder, IEEE Transactions on Computers 42 (12) (1993) 1495–1499

#### Books:

CMOS Digital integrated circuits Analysis and Design by SUNG-MO KANG