# A Study of JK and T Flip Flops with and without Delay Using QCA

Aditi Bal, Subhashree Basu, Supriyo Sengupta,

<sup>1</sup>Department of Information Technology, St. Thomas College of Engineering and Technology, khidirpore, India <sup>2</sup>Department of Computer Science and Engineering, St. Thomas College of Engineering and Technology, khidirpore, India <sup>3</sup>Department of Electronics and Communication Engineering, St. Thomas College of Engineering and

<sup>3</sup>Department of Electronics and Communication Engineering, St. Thomas College of Engineering and Technology, khidirpore, India

**Abstract:** As transistors decrease in size, more and more of them can be accommodated in a single die, thus increasing chip computational capabilities. However, transistors cannot get much smaller than their current size. The use of quantum dots instead of CMOS transistors for implementing digital system at nanolevel is becoming more and more popular because of its faster speed, smaller size and low power consumption. Many interesting QCA-based logic circuits with smaller feature size, higher operating frequency, and lower power consumption than CMOS have been presented, even though the design of logic modules in QCA is not always straightforward. In this paper, the basic sequential logic structures-JK and T flip-flops are discussed based on QCA design, with comparatively less number of cells and area. Such devices are expected to function with ultra low power consumption and very high speed. Along with it, a design for T flip-flop with a delay is compared with a T flip-flop without any delay. The simulation result clearly testifies the validity of T flip-flop with delay.

Additional Key Words and Phrases: CMOS, flip-flops, QCA

#### I. Introduction

In the past few decades, CMOS technology has consistently played a vital role in implementing high density, high speed and low power VLSI systems. However, several studies have predicted that these technologies are approaching their physical limits.QCA can prove to be an attractive alternative. It is expected to achieve high device density, extremely low power consumption and very high switching speed.QCA structures are built as an array of quantum cells within which each cell has an electrostatic interaction with all its neighboring cells. In QCA, polarization, instead of traditional current contains the digital information. Though there are numerous advantages provided by QCA there are some challenges identified by Kogge[7]. One of them is the lack of feed- back. The 4-phase clocking scheme flows data in one direction. Physical feedback is essential in designing sequential circuits as the next state is dependent on the present state. Inclusion of feedback loops in QCA designs may result in complex clocking zone structure and floor planning. By introducing a delay, the global synchronization re- mains intact but a local asynchronous system can be introduced between cells and thus the feedback path functions accurately. The basic logic elements used in this technology are the inverter and the majority gate. The other logical structures are designed using these basic elements[4; 5; 10].

### 1.1. QCA Basics

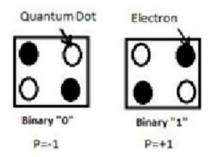

QCA[2; 8] is a new device architecture that is amenable to nanometer scale. The QCA stores logic states not as voltage levels but rather based on the position of individual electrons. A quantum cell[3] can be viewed as a set of four charge containers or dots that are positioned at the corners of a square cell. Computation is realized by the Coulombic interaction of extra electrons in the quantum dots[6]. Each quantum dot is a nanometer-scaled square with wells at each corner of the cell. The two extra electrons that are present in each cell can quantum-mechanically tunnel between wells, but they cannot tunnel out of the cell. Provided that the electrons will always tend to occupy antipodal sites, there are two possible configurations as shown in the figure 1.

A:2 S. Basu et al.

Fig. 1. Basic QCA cell and Two Possible Polarizations

#### 1.2. QCA Clocks

The traditional CMOS clock and QCA clock[15; 16; 17] are quite different. In CMOS

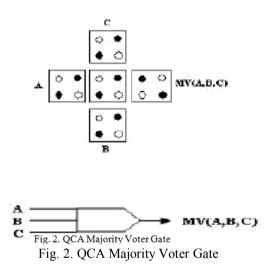

the circuit with a clock is known as sequential circuit. But in QCA the clock is provided to ensure the flow of data even it is a combinational circuit[14; 22; 24; 18; 19; 20; 21; 23; 1]. The fundamental QCA logical circuit is the three-input majority gate[11; 12; 13] (figure 2). Computation is performed with the majority gate by driving the device

Cell to its lowest energy state. This occurs when it assumes the polarization of the majority of the three input cells. Clock zones are a tricky challenge of QCA. They avoid random adjustments of QCA cells and "guide" the information flow, in particular the data propagation, through QCA circuits. In contrast to transistor-based circuits, one clock cycle consists of four clock signals, which are delayed by of the whole clock cycle among each other, as depicted in figure 3. To ensure QCA circuits close to a ground state, a widely adopted clocking scheme is adiabatic switching which utilizes an adiabatic periodic signal with four different phases: switch, hold, release, and relax. When the potential is low the electron wave functions become delocalized resulting in no definite cell polarization. Raising the potential barrier decreases the tunneling rate, and thus, the electrons begin to localize. As the electrons localize, the cell gains a definite polarization. When the potential barrier has reached its highest point, the cell is said to be latched. Latched cells act as virtual inputs and as a result, the actual inputs can start to feed in new values. With the barriers lowering slowly, the electrons gradually become free and the cell starts to lose its polarization. During the relax

A Study of JK and T Flip Flops with and without Delay Using QCA

A:3

phase, the barriers are low, the electrons are free to tunnel and delocalize, and the cell has no polarization, i.e., P=0.

## II. Flip-Flops

Flip-flops and latches are fundamental building blocks of sequential digital circuits where clock playing an important role to control the output[9]. In QCA we don't have any control over clock pulse.

### 2.1. JK Flip-flop

The JK flip-flop is a refinement of the RS flip-flop in that the indeterminate state of the RS type is defined in JK type. Only when inputs are applied to both J and K simultaneously, the flip-flop switches to its complement state i.e. if Q=1,it switches to Q=0 and vice-versa. Because of the feedback connection in the JK flip-flop,the clock sig- nal CP which remains at 1 after the outputs have been complemented once will cause repeated and continuous transitions of the outputs. To avoid this undesirable opera- tion,the clock pulse must have a time duration which is shorter than the propagation delay through the flip-flop.In the proposed design, clock is considered in the characteristic equation so that it can have a definite impact. Not only the clock pulse but also the preset input is also considered to get the initial output. The new characteristic equation is obtained from the following table.

#### Table I. Truth table of JK Flip-flop

| Р | CP | Q | J | K | Q(t+1) |

|---|----|---|---|---|--------|

| 0 | X  | Х | х | Х | 1      |

| 1 | 0  | 0 | x | x | 0      |

| 1 | 0  | 1 | x | x | 1      |

| 1 | 1  | 0 | 0 | 0 | 0      |

| 1 | 1  | 0 | 0 | 1 | 0      |

| 1 | 1  | 0 | 1 | 0 | 1      |

| 1 | 1  | 0 | 1 | 1 | 1      |

| 1 | 1  | 1 | 0 | 0 | 1      |

| 1 | 1  | 1 | 0 | 1 | 0      |

| 1 | 1  | 1 | 1 | 0 | 1      |

| 1 | 1  | 1 | 1 | 1 | 1      |

To simplify it, Karnaugh map is used and we get  $Q(t+1) = P^{\Box}' + CP^{\Box}' Q + K' Q + CP Q' J.$

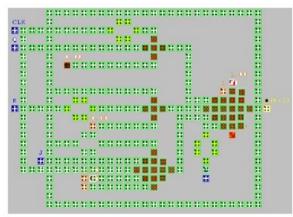

The circuit diagram of JK flip-flop using basic QCA gates is shown below.

Fig. 4. Circuit Diagram of JK flip-flop

Fig. 5. Layout Diagram of JK flip-flop

S. Basu et al.

(1)

A Study of JK and T Flip Flops with and without Delay Using QCA

#### 2.2. T Flip-flop

The T flip-flop is a single-input version of the JK flip-flop. The t flip-flop is obtained from a JK type if both inputs are tied together. The designation T comes from the ability of the flip-flop to "toggle" or change state. Regardless of the present state of the flip-flop, it assumes the complement state when the clock pulse occurs while input T is logic 1. The traditional T flip flop has the following characteristic equation as given by.

$Q(t+1) = T^{\Box} Q' + T Q' = T^{\Box} \Theta Q.$

(2)

(3)

A:5

The QCA cannot follow the traditional T flip flop design as to provide a feedback path is a major challenge. The truth table, taking the clock pulse and the preset input into consideration is shown below.

Table II. Truth table of T Flip-flop

| P | CP | Q | Т | Q(t+1) |

|---|----|---|---|--------|

| 0 | X  | Х | Х | 1      |

| 1 | 0  | 0 | х | 0      |

| 1 | 0  | 1 | x | 1      |

| 1 | 1  | 0 | 0 | 0      |

| 1 | 1  | 0 | 1 | 1      |

| 1 | 1  | 1 | 0 | 1      |

| 1 | 1  | 1 | 1 | 0      |

The logical expression for T flip-flop is reduced to

$$Q(t+1) = P^{\Box}' + CP^{\Box}' Q + Q' T + CP Q T^{\Box}'$$

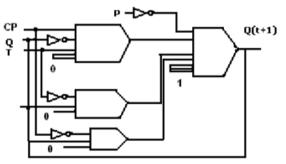

The circuit diagram of T flip-flop using basic QCA gates is shown below.

Fig. 6. Circuit Diagram of T flip-flop

### A:6 S. Basu et al.

Fig. 7. Layout Diagram of T flip-flop

### III. Result Analysis

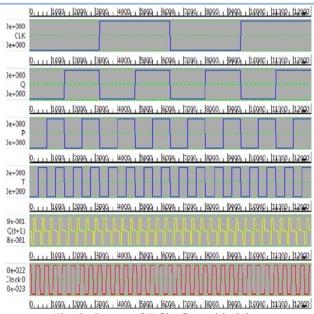

In the proposed design, clock is considered in the characteristic equation so that it

can have a definite impact. The advantage of introducing independent CP is that the design of QCA sequential circuits may be simplified by reducing the attention to timing constraints. Not only the clock pulse but also the preset input is also considered to get the initial output. At first the proposed T flip flop is designed which is synchronous to the global clock provided by the QCAdesigner. From the output of T flip flop it is very

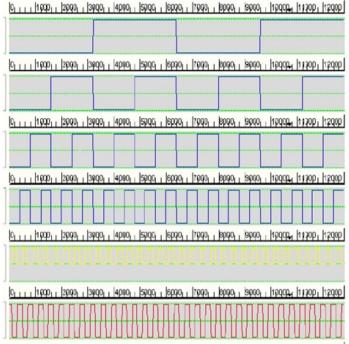

Fig. 8. Output of T flip-flop without delay

A Study of JK and T Flip Flops with and without Delay Using QCA

A:7

Clear that the flip flop cannot hold a value. To overcome the latching problem an OR gate is introduced where the local cell clock is considered as clock 3 if QCA designer whereas the initial state is provided with clock 0. This setup provides a 3/4th delay to the output in compare to the input.

#### IV. Conclusion

In the case of current driven circuits, when have a feedback loop, the current gives the needed directionality. It ensures the fact that to start at the input and end at the output going through a series of voltage changes along the way. However, in this case, there is no current and no directionality. It is a system which waits to settle in a stable ground state. This means that the concept of feeding output back into the input is equivalent to actually feeding the input into the output since there is no question of direction. From the simulated output it is very much clear that the T flip flop without a delay cannot hold the value. Where as if we introduce a extra OR gate with a global clock with 3/4th T lagging with the starting clock to asynchronize the charge flow the output is convincing. By introducing another OR gate may increase number of cell count but looking at the output it may be considered.

#### References

- S.M.Wu.," A [1]J realize a'la'. new approach to partially symmetric unctions". Tech.Rep. SRCTR86-54, Dept.EE, University of Maryland, 1986.

- [2] C. S. Lent, P. D. Taugaw, W. Porod, G. H. Berstein.," Quantum Cellular Au- tomata.Nanotechnology", vol. 4, no. 1, pp49-57, January 1993.

- A. O. Orlov, I. Amlani, G. H. Bernstein, C. S. Lent, G. L.Sinder.," Realization of a Functional Cell for Quantum Dot Cellular [3] Automata", Science, vol. 277, no. 5328, pp 928-930, August 1997.

- [4] C. S. Lent, P. D. Taugaw." A Device Architecture for Computing with Quantum Dots", Proceedings IEEE, vol. 85, no. 4, pp.541-557, April 1997

- [5] I. Amlani, A. O. Orlov, G. Toth, C. S. Lent, G. H. Bernstein, G. L.Sinder.," Digital Logic Gate using Quantum Dot Cellular Automata", Science, vol. 284, no. 5412, pp. 289-291, April 1999.

- G.Snider, A. Orlov, I Amlani, G. Bernstein, C. Lent, J. Merz and W. Porod, "Quantum- Dot Cellular Automata," Microelectronic [6] Engineering, Vol 47, pp 261-263, 1999

- [7] M.Niemier and P. Kogge,"Problems in Designing with QCAs: Layout Equals Timing," International Journal of Circuit Theory and Applications, Vol 29, pp 49-62, 2001

- M. Lieberman, S. Chellamma, B. Varughese, Y. Wang, C. S. Lent, G.H. Bernstein, G.L.Snider, F. Peiris.," Quantum Dot [8] Cellular Automata at a Molecular Scale", Annals of the New York Academy of Sciences, vol. 960, pp. 225-239,2002.

- Anoop Vetteth, Konrad Walus, Vassil S. Dimitrov, Graham A. Jullien, "Quantum-dot cellular automata of flip-flops",9th [9] International conference on communications, pp- 368 - 372, Jan 2003 Whitney J. Townsend, Jacob A. Abraham." Complex Gate Implementations for Quan- tum Dot Cellular Automata", 4th IEEE

- [10] Conference on Nanotechnology, pp. 625-627, August 2004.

- R. Zhang, K.Walus, W.Wang, G.A.Jullien.," A Method of Majority Logic Reduction for Quantum Cellular Automata", IEEE Trans on Nanotechnology, vol. 3, no. 4, pp. 443- 450, Dec 2004. [11]

- K. Walus, G. Schulhof, G. A. Jullien, R. Zhang, W. Wang.," Circuit Design Based on Majority Gates for Application with [12] Quantum Dot Cellular Automata", IEEE Trans Signals, Systems and Computers, vol. 2, pp. 1354-1357, Nov 2004

- M. Momenzadeh, M. B. Tahoori, J. Huang, F. Lombardi," Characterization, Test and Logic Synthesis of AND-RINVERTER [13] (AOI) Gate Design for QCA Implementa- tion", IEEE Trans on Computer Aided Design of Integrated Circuits and Systems, vol. 24, no.,pp. 1881-1893, December 2005.

- [14] H. Rahaman, B. K. Sikdar, D.K. Das." Synthesis of Symmetric Boolean Functions Using Quantum Cellular Automata", International Conference on Design and Test of Integrated Systems in Nanoscale Technology (DTIS 06), pp.119-124, Tunis,

- [15] Kolin Paul. Quantum Cellular Automata. Thesis submitted to Indian Institute of Technology, Delhi an exciting blend of Computer Science and Physics-2006.

- Z. Y. Xu , M. Fenga , W. M. Zhang," Universal Quantum Computation With Quantum- Dot Cellular Automata In Decoherence-[16] Free Subspace", Quantum Information and Computation, Vol. 0, No. 0000-000c Rinton Press, 2008.

- Mostafa Rahimi Azghadi\*, O. Kavehei, K. Navi."A Novel Design for Quantum-dot Cellular Automata Cells and Full Adders" [17]

- [18] Heumpil Cho." Adder Designs and Analyses for Quantum-Dot Cellular Automata", IEEE Transactions on Nanotechnology, Vol. 6, No. 3, May 2007

- [19] Heumpil Cho, Earl E. Swartzlander." Adder and multiplier Design in Quantum-Dot Cellular Automata", IEEE Transactions on Computers, Vol. 58, No. 6, Jun 2009

- [20] Geza Toth\*, Craig S. Lent." Quantum computing with quantum-dot cellular au- tomata", Physical Review A, Volume 63, 052315

- [21] Pijush Kanti Bhattacharjee." Use of Symmetric Functions Designed by QCA Gates for Next Generation IC", International Journal of Computer Theory and Engineering, Vol. 2, No. , April 2010 1793-8201

- [22] Hema Sandhya Jagarlamudi, Mousumi Saha, Pavan Kumar Jagarlamudi." Quantum Dot Cellular Automata Based Effective Design of Combinational and Sequential Logical Structures", World Academy of Science, Engineering and Technology 60, 2011.

- [23] C.Rovetta M.Mouffron." De Bruijan sequences and complexity of symmetric functions", Cryptography and Communications journal, vol.3, no. 4, pp.207-225,(December,2011).

- [24] S. Basu, S. Bhattacharjee." Implementation of Symmetric Functions Using Quantum Dot Cellular Automata", ICACNI,2014